### Regular Article

## High-Level Modeling and Simulation of a Novel Recon gurable **Network-on-Chip Router**

#### Thanh-Vu Le-Van, Xuan-Tu Tran

SIS Laboratory, VNU University of Engineering and Technology, Cau Giay, Hanoi, Vietnam

Correspondence: Xuan-Tu Tran, tutx@vnu.edu.vn

Manuscript communication: received 28 July 2014, accepted 02 January 2015

Abstract- In this paper, we present a novel router architecture for implementing a Recon gurable Network-on-Chip (RNoC) at high-level design using SystemC. The RNoC is an adaptive NoC-based system-on-chip providing a dynamic recon gurable communication mechanism. By adding a virtual port - named Routing Modi cation port - into the conventional router architecture, the network router is able to route communication data exibly whenever the target routing path is blocked, by unwanted defects or intently by a software programme to meet the requirements of applications. The proposed architecture has been modeled in SystemC/C++, simulated and veri ed within a 2D mesh  $5 \times 5$  network platform. In normal communication mode, the static XY routing algorithm is used while the West-First algorithm with a proposed prohibited router surrounding technique will be applied in recon guration mode. Experimental results are also reported to compare the performance of the network architecture in different operation modes as well as with the other works.

34

35

36

37

44

47

49

50

54

56

57

58

59

Keywords- Network-on-Chip, Recon guration, High-level modeling.

#### **1** INTRODUCTION

The conventional shared-bus design methodology 2 could not meet the increasingly needs of the on-chip 3 communication in System-on-Chips (SoCs) because of 38 4 long-wire loads, resistances and shared bandwidth. The 5 bus hierarchical architecture has become an alternative <sup>40</sup> 6 solution but still faces many constraints in on-chip 41 7 interconnections due to shared-bus s limitations.

The Network-on-Chip (NoC) paradigm has been 43 9 known as an emerging design methodology for billion-10 transistors SoCs thanks to many advantages: high 11 communication throughput, exibility and scalability, 12 power management efficiency, etc. [1]. In NoC-based 13 systems, hundreds of processing cores (i.e., Intellectual 14 Properties (IPs)) have been integrated into a single sys-15 tem to meet the increasingly demand of applications. 16 This leads to many challenges in system design. One 17 of these challenges is how to make the system adaptive 18 to the need of target applications at a specific time or 19 adaptive to the faults appeared during the operation. It 52 20 means that the system should be able to be reconfigured 53 21 at run-time. 22

In this paper, we present a novel reconfigurable 55 23 router architecture for 2D mesh NoCs implementation. 24 The network router is able to route communication 25 data exibly thanks to a virtual port – named Routing 26 Modification (RM) port. With this design, the network 27 router is dynamically reconfigured whenever the target 60 28 routing path is blocked, by unwanted defects or intently 61 29 by a software programme to meet the requirements of 62 30 applications. The proposed network router is then used 63 31 to build a 2D mesh  $5 \times 5$  Reconfigurable Network-on- <sup>64</sup> 32 Chip (RNoC) platform for validation purpose. All the 65 33

platform has been modeled, simulated and verified at high level using SystemC, a C/C++ library for hardware modeling. The static XY routing algorithm has been used in the normal communication mode while the West-First algorithm with a proposed prohibited router surrounding technique has been applied in the reconfiguration mode.

The remaining part of the paper is organized as follows. Section 2 provides a brief review on the related works. Section 3 introduces the proposed reconfiguration solution which allows modifying routing information to adapt real situations of the network. In Section 4, we present the proposed architecture for reconfigurable router, which is used to build the RNoC. Simulation and experimental results of a 2D mesh  $5 \times 5$  RNoC are given in Section 5. Finally, conclusions will be provided in Section 6.

#### **2** Related Works

There are three main concerns in implementing reconfigurable NoCs: reconfiguration administration, reconfiguration infrastructure, and reconfiguration protocols [2]. The first issue defines the administration methods including decision, validation, and execution. The second and the third ones relate to the changes on the network structure and network protocol, respectively.

As the communication is decoupled from the computation in NoC-based systems, the design of network infrastructure and protocol should be considered to increase the systems exibility and reconfigurability. In [3], a reconfigurable NoC infrastructure was developed to make the system interconnection more exible. This work aims at providing a reconfigurable

interconnection architecture for FPGA implementation. 66 The work presented in [4] introduced a reconfigurable 67 mechanism for NoC architectures to provide fault tol-68 erance. The uLBDR (Universal Logic-Based Distributed 69 Routing) is proposed as an efficient logic-based mech-70 anism to adapt to irregular topologies for 2D mesh 71 networks. The main advantage of this proposal is 72 the exibility in routing communication information. 73 However, it is obvious that we need more hardware 74 resources for implementing the network routers. The 75 work, presented in [5], proposed a hybrid communica-76 tion reconfigurable NoC architecture. By using special 77 wrappers surrounded the network routers, the network 78 topology can be modified to adapt the requirements of 79 applications. In [6], Stuart et al. proposed ReNoC router 80 architecture with a special circuit switching wrapper 81 which is used to change the network topology. ReNoC 124 82 83 architecture uses an optimization algorithm with the 125 initial topology of the network to match the target 126 84 application. Therefore, this work must use application- 127 85 specific routing and needs an initial phase to configure 128 86 87 the topology before the system operates. In [7], ViChaR 129 architecture was proposed to exibly store data its 130 88 into buffers at INPORT modules. However, the area 131 89 overhead is a drawback of this proposal. In another 132 90 work [8], Lan *et al.* proposed a router architecture al- 133 91 lowing each communication channel to be dynamically 134 92 self-reconfigured to transmit data in either direction 135 93 in order to better utilize on-chip hardware resources 136 (therefore, enhance the performance of on-chip com- 137 95 munication). The disadvantage of this proposal is that 138 96 it leads to the complexity of routing algorithms. In all of 139 97 the above proposals, the reconfiguration administration 140 98 has been distributed at the network routers. 99

Related to the routing algorithm of reconfigurable 142 100 NoCs, in [3], Bobda et al. proposed a Surrounding XY 143 101 routing algorithm to surround obstacle components. 144 102 The DyNoC router has three operation modes: N- 145 103 XY (Normal XY routing), SH-XY (Surround Horizontal 146 104 XY routing) and SV-XY (Surround Vertical routing). 147 105 By combining deterministic and adaptive routing, Hu 148 106 and Marculescu [9] presented DyAD which is smart 149 107 routing to adapt network status. Manevich et al. [10] 150 108 used a centralized routing control module to change XY 151 109 routing or YX routing while the work in [4] introduced 152 110 a Logic Based Distributed Routing (LBDR) algorithm, 153 111 LBDR<sub>fork+dr</sub>. This is an efficient routing to adapt to 154112 irregular topologies of 2D mesh networks. 113 155

# <sup>114</sup> 3 Proposed Reconfiguration Solution<sup>115</sup> AND ROUTING ALGORITHMS

Many NoC architectures have been developed by re- 161 116 search groups, at both university and industry sectors. 162 117 However, the most dominant topologies used in those 163 118 NoC architectures are 2D mesh or 2D torus because 164 119 of their semiconductor implementation. In our work, 165 120 we focus on 2D mesh NoC architectures with source, 166 121 deterministic routing. The target NoC architecture has 167 122 been presented in [11]. 123

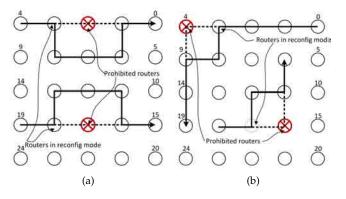

Figure 1. Update the routing path when the prohibited router appears: at the middle of a straight segment of the routing path (a) or at the corner of the routing path (b).

In 2D mesh NoC architectures, the static XY routing algorithms route communication data following straight routing segments and routing corner [12]. A routing corner appears when the routing path changes the direction from X to Y. When there is a prohibited router on the routing path, the communication data has to be routed around the prohibited router. It means that the related routers must be reconfigured to change the routing path to avoid the prohibited router. In this situation, depending on the position of the prohibited router and the destination router, the routing path should be modified in different strategies in order to ensure that the communication data will reach to the destination router with a minimum cost. By exploring 2D mesh NoC architectures, we can divide the reconfiguration strategy into 3 cases:

**Case 1**: The prohibited router appears at the middle of a straight segment of the routing path (see Figure 1(a)). In this case, the routing path has to be changed at the router before the prohibited router to avoid the prohibited router. The main principle is the communication data is routed to the left or the right routers instead of the prohibited router (the West-First routing algorithm is preferred in our experiment). Then the communication data will be forwarded by two hops with the same direction as the old routing path (normal routing path) before it is given back to the old routing path. In this case, we need two more hops in the new routing path (one to avoid the old routing path and one to come back to the old routing path). The router before the prohibited router must be reconfigured to add and update the routing information for 5 related hops (one hop needs to be updated, two hope need to be added, and the middle one and the last one can be kept). The old routing path is depicted as dot line and the new routing path (reconfigured routing path) is depicted as continuous line.

156

157

158

159

160

**Case 2**: The prohibited router appears at the corner of the routing path. The routing path is also changed to avoid the prohibited router as depicted in Figure 1(b). The dot line describes the old routing path and the continuous line describes the new (reconfigured) routing path. However, in this case there are only three routers affected by the reconfiguration to establish the new routing path, even if the routing corner appears at the

Figure 2. Update the routing path when the prohibited router appears just before or just after the corner of the routing path.

corner of network architecture. The router placed before

the prohibited router must be reconfigured to change

the routing information for three hops in corresponding

to three related routers.

**Case 3**: The prohibited router appears just before or 173 just after the corner of the routing path. Figure 2(a) 174 illustrates the case that the prohibited router appears 175 before the corner of the routing path and Figure 2(b) 176 illustrates the case that the prohibited router appears 177 after the corner of the routing path. Similar to the two 178 cases above, the routing path is also changed to avoid 179 the prohibited router. However, in this case there are 180 four routers affected by the reconfiguration to establish 181 the new routing path. The West-First routing algorithm 182 is also preferred in changing the routing direction. The 183 router before the prohibited router has to be reconfig- 219 184 ured to change the routing information for four hops 185 220 (if the prohibited router appears before the corner of 221 186 the routing path) or five hops (if the prohibited router 222 187 appears after the corner of the routing path). In the 223 188 case 3a, one hop needs to be updated, one hop needs 189 224 to be added, and two last ones can be kept). In the case 190 225 3b, one hop needs to be updated, two hops need to be 191 226 added, the middle one and the last one can be kept. 192 227

There is a special case, when the destination router response to the probibited router). The communication data cannot reach response to its destination and therefore should be deleted to rincrease network load. This is also considered in our proposal.

With deterministic, source routing NoC architectures, 199 234 the routing information is stored in "Path-to-Target" 200 field of the header it [11]. Therefore, to change the 236 201 routing path the network router should be able to 237 202 update/modify the routing information in "Path-to-203 Target" field. That s why we have proposed a novel 204 router architecture for reconfigurable NoCs as pre-205 240 sented in the next section. 206 241

#### 207 4 Reconfigurable Router Architecture

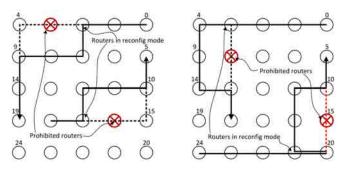

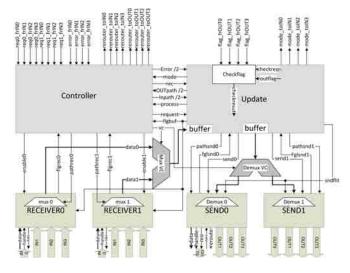

In this work, we propose a novel architecture for the <sup>245</sup>

network router used in reconfigurable Network-on- <sup>246</sup>

Chips, depicted in Figure 3. The proposed reconfig- <sup>247</sup>

urable network router is composed of five INPORT <sup>248</sup>

modules, five OUTPUT modules, and a virtual Rout- <sup>249</sup>

ing Modification (RM) port. Four INPORT/OUTPORT <sup>250</sup>

Figure 3. The proposed reconfigurable network router.

pairs are connected to four neighbour routers and the remaining pair (local INPORT/OUTPORT) is connected to the nearest IP core. The virtual RM port is used for reconfiguration purpose. These modules are connected together through two signals matrix for two virtual channels. The local INPORT has a signal vector to indicate the status of OUTPORT modules; and the local OUTPORT has four ag signals to inform the status of INPORT modules.

There are two operation modes of the router: normal mode and reconfig mode. In normal mode, a data packet is received at INPORT and will be sent to next router through the target OUTPORT for all its in the packet. In reconfig mode, INPORT received a header it, but it cannot be sent to selected OUTPORT because the selected OUTPORT is blocked. Therefore, the IN-PORT changes its operation mode, then sends header it to the RM port and waits for the response from the RM port. At the RM port, the routing information ("Part-to-Target" field) of the header it will be changed so that the header it is sent to a new OUTPORT; the RM port sends a command back to the INPORT to control the sending of the body its of the packet (these its will be routed to the new OUTPORT instead of the previously selected OUTPORT).

The detail of INPORT structure is shown in Figure 4. This work supports communication with two virtual channels (0 and 1), so that INPORT has subblocks corresponding virtual channels: RouteVC0 & RouteVC1, Sendacc0 & Sendacc1. The VC\_Demux subblock is used to receive it and give routing information at "Path-to-Target" field in normal mode. When the selected OUTPORT is blocked, the Prohibited Control sub-block detects and sets the mode of INPORT into reconfig mode. When a cell is prohibited, this sub-block receives status ag from LOCAL port and then it prohibits the OUTPORT module which is connected to it.

242

243

244

Figure 4. Micro-architecture of INPORT modules.

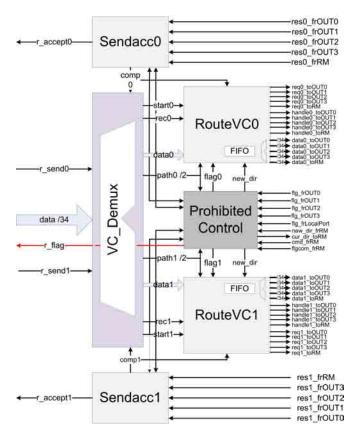

OUTPORT module has eight sub-blocks and supports two virtual channels as described in Figure 5. There are three pair sub-blocks supporting two virtual channels, such as: Arbiter0 & Arbiter1, Forward0 & Forward1, and MuxVC0 & MuxVC1.

251

The VC-Mux sub-block is used to combine two vir-257 tual channels and to send data to next router. At the 258 Arbiter sub-blocks, we use First In-First Served (FIFS) 259 mechanism when there are more than one request from 260 INPORT modules. The OUTPORT goes into reconfig 261 mode when it receives a request from RM port, and 262 then the Prohibited Control sub-block actives ag to 263 control other sub-blocks in reconfig mode. At reconfig 264 mode, the OUTPORT receives header it from RM port 265 and command to forward other its of data packet. 266 If RM port only sends header it, the response of 267 OUTPORT is changed to INPORT which is indicated 268 from RM port. 269

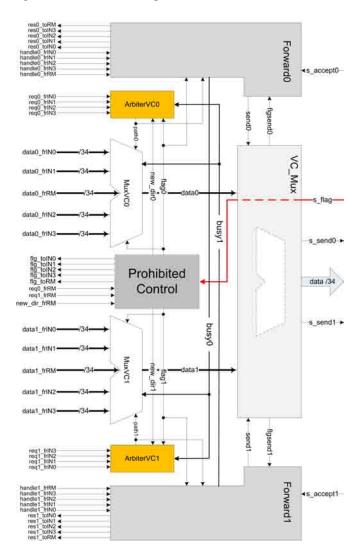

The architecture of the virtual RM port is shown in 270 Figure 6. In this virtual port, two sub-blocks, Receiver0 271 and Receiver1, are used to receive its from INPORT 272 modules and two sub-blocks, Sender0 & Sender1, send 273 its to OUTPORT modules for virtual channels 0 & 1, 274 respectively. The Controller sub-block is used to control 275 the sub-blocks in RM port and receives request from 276 INPORT modules. The process which is used to change 277 routing information in "Path-to-Target" field and se-278 lected new OUTPORT is implemented in the Update 283 279 sub-block. In the Update sub-block, we use small sub- 284 280 block to check the status of OUTPORT modules in 285 281 282 router. The checking results are used to select a possible 286

Figure 5. Micro-architecture of OUTPORT modules.

Figure 6. Architecture of the virtual Routing Modification (RM) port.

OUTPORT to forward data into previous router in the new routing path. In this work, the RM port is equivalent to a virtual port, it only use one buffer for two virtual channels.

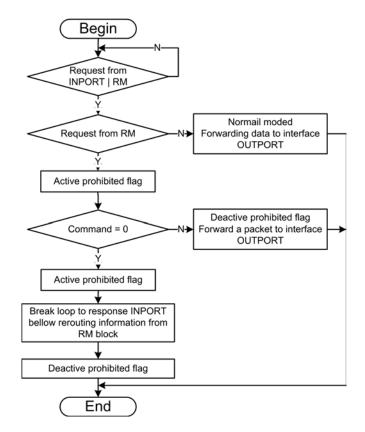

Figure 7. Operation owchart of INPORT.

#### <sup>287</sup> 5 Simulation and Experimental Results

The simulated platform was configured in 2D mesh topology with  $5 \times 5$  network size. We use complement

communication pattern and source static XY routing 322 290 algorithm to generate data packet and inject into net- 323 291 work from stimulating IP cores [13]. When RNoC is 324 292 simulated, we control it to change prohibited cell (ob- 325 293 tain IP core and router) and network load is injected 326 294 into network. After simulating RNoC, the evaluation 327 295 is executed to compute network latency and average 328 296 throughput. 329 297

The operation of INPORT modules is shown in Figure 7 and the owchart describes operation of OUT-PORT in Figure 8.

The reconfig mode is started at INPORT and is pro- 333 301 cessed at RM port in the router. When the correspond- 334 302 ing OUTPORT is blocked, the Prohibited Controller 335 303 sub-block release an active mode ag and controls 336 304 other sub-block in the reconfig mode. The header it 337 305 is forwarded to RM port, after INPORT waits until 338 306 the RM port completely processes the header it. If 339 307 mode frRM signal is not active, INPORT will forward 340 308 other its of packet to a new OUTPORT that is selected 341 309 from RM port. 310 342

At OUTPORT module, the reconfig mode is started <sup>343</sup> when it is requested from RM port, the Prohibited Controller controls other sub-block of OUTPORT module. <sup>345</sup> If mode\_frRM is not active, the OUTPORT interrupts <sup>346</sup> response for RM port and then the RM port informs <sup>347</sup> the INPORT to send other body it of packet. <sup>348</sup>

The RM port is active when there are any requests <sup>349</sup> from INPORT modules. The RM port receives data <sup>350</sup> it similar OUTPORT mechanism and stores it into <sup>351</sup> receiver buffer. Base on routing the current information <sup>352</sup> routing in "Path-to-Target" field, the ID of INPORT, and <sup>353</sup>

Figure 8. Operation owchart of OUTPORT.

the ID of the error OUTPORT, the Update sub-block decides a new corresponding OUTPORT and modifies routing information. After completing the process for header it, RM port sends the header it to OUTPORT and a command to INPORT to ask the INPORT to go into reconfig mode. In the normal mode, the RM port is not used; the data packets will be transferred from INPORT through OUTPORT modules.

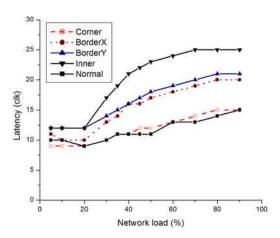

To show the difference between normal mode and reconfig mode of the proposed RNoC, we compare the communication performance in terms of latency and throughput of these modes with different positions of prohibited router. Figure 9 shows the relationship between the network latency and the network load with normal mode (Normal) and different reconfig modes (Corner, BorderX, BorderY, and Inner). In the figure, the latency of normal mode is lowest and the latency of reconfig mode in which the Inner router is prohibited (see Figure 1(a) for router location) is highest. In fact, when the Inner router is prohibited, four directions will be blocked. As a result, many packets are blocked in routing paths; thus there are many routing paths which are reconfigured. When the prohibited router is placed at the Corner or the Border, the network latency is less than in the Inner cases.

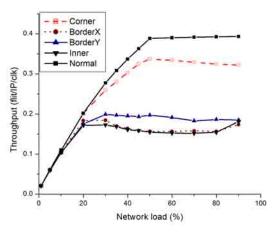

The communication throughput in corresponding with the network load is presented in Figure 10. We can see that when the network load is small enough, the throughput in reconfig mode is similar to the throughput of normal mode. When a prohibited router is located at the network boundary, the throughput is slightly reduced. In the worst case, the throughput sat-

Figure 9. The network latency in corresponding with the network load.

Figure 10. The network throughput in corresponding with the <sup>379</sup> network load.

urates at 0.16 *it/IPcore/clk* when network load is equal  $\frac{382}{383}$  to 30%.

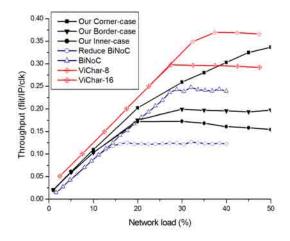

The obtained simulation results have been also com-356 pared with the previous works as depicted in Figure 11. 386 357 From this comparison, we can see that the ViChar 387 358 proposal [7] has a better communication throughput. 388 359 However, the implementation of this solution is more 389 360 expensive than our proposal in terms of area overhead, 390 361 each router needs 40 or 80 its buffering for ViChar-8 or 391 362 ViChar-16, respectively. In addition, they use 4 virtual 392 363 channels for each physical communication channel. 393 364 The Reduced BiNoC [8] has a lowest communication 394 365 throughput even the total buffer size is the biggest. Our 366 395 proposal has a high throughput when the prohibited 367 router is placed at the corner of the network. In the 368 worst case, the prohibited router is an inner router, 396 369 the achieved throughput is nearly the same as ViChar-370 8/ViChar-16 when the network load is less than 20% 397 371 and acceptable when the network load is greater than 398 372 20%. The details of each architecture has been reported 399 373 374 in Table I. 400

Figure 11. Throughput comparison with the previous works.

Table I Communication Resource for Each Router (RNoC, ViChar, and BiNoC)

| Architectures     | our<br>RNoC     | BiNoC<br>[8]   | Re. BiNoC<br>[8] | ViChar-8<br>[7] | ViChar-16<br>[7] |

|-------------------|-----------------|----------------|------------------|-----------------|------------------|

| Total # buffers   | 6               | 10             | 5                | 5               | 5                |

| Buffer/Direction  | 1               | 2              | 1                | 1               | 1                |

| Each buffer size  | 2 flits         | 16 flits       | 32 flits         | 8 flits         | 16 flits         |

| Total buffer size | 12 flits        | 160 flits      | 160 flits        | 40 flits        | 80 flits         |

| Crossbar          | $2(6 \times 6)$ | $10 \times 10$ | $5 \times 5$     | $5\times5$      | $5\times5$       |

| Ports             | 5+1             | 10             | 5                | 5               | 5                |

| Virtual channels  | 2               | 2              | 1                | 4               | 4                |

### 375 6 Conclusions

376

377

378

381

We have presented the routing method and the design of a reconfigurable router which can be used for implementing a reconfigurable Network-on-Chip (RNoC). The design has been modeled at high-level using SystemC. By adding a virtual Routing Modification port (RM port) into the router architecture, the network router is able to route communication data exibly whenever the target routing path is blocked to meet the requirements of reconfiguration or to adapt the working situation caused by unwanted defects. The proposed architecture has been simulated and verified within 2D mesh  $5 \times 5$  network platform. In this verification platform, the static XY routing algorithm has been used in the normal communication mode while the West-First algorithm and a proposed prohibited router surrounding technique have been applied in the reconfig mode. The experimental results show that our proposed solution provide a better communication performance in terms of throughput and latency with a smaller hardware resource.

#### ACKNOWLEDGMENT

This work is supported by the research project "Reconfiguration Solution in Designing Network-on-Chip Architectures (ReSoNoC)" (No. 102.01-2013.17) granted by Vietnam National Foundation for Science and Tech74

421

447

nology Development (Nafosted). 401

#### References 402

- 474 [1] L. Benini and G. De Micheli, "Networks on chips: a new 403 475 SoC paradigm," Computer, vol. 35, no. 1, pp. 70-78, Jan 404 476 2002. 405

- [2] R. Dafali, J.-P. Diguet, and M. Sevaux, "Key research 406 478 issues for reconfigurable network-on-chip," in Proceed-407 479 ings of the 2008 International Conference on Reconfigurable 480 408 Computing and FPGAs (ReConFig), Cancun, December 481 409 2008, pp. 181–186. 410

- [3] C. Bobda, A. Ahmadinia, M. Majer, J. Teich, S. Fekete, 483 411 484 and J. van der Veen, "DyNoC: A dynamic infrastruc-412 ture for communication in dynamically reconfigurable 413 devices," in Proceedings of the International Conference on 414 Field Programmable Logic and Applications, August 2005, 415 pp. 153–158. 416

- [4] S. Rodrigo, J. Flich, , A. Roca, S. Medardoni, D. Bertozzi, 486 417 J. Camacho, F. Silla, and J. Duato, "Addressing man- 487 418 ufacturing challenges with cost-efficient fault tolerant 488 419 routing," in Proceedings of the 4th ACM/IEEE International 489 420 Symposium on Networks-on-Chip, Grenoble, France, May 490 491 2010, pp. 25-32. 422

- 423 [5] L. Zheng, C. Jueping, D. Ming, Y. Lei, and L. Zan, "Hybrid communication reconfigurable network on chip 424 494 for MPSoC," in Proceedings of the 2010 IEEE International 425 495 Conference on Advanced Information Networking and Appli- 496 426 cations (AINA), Perth, WA, April 2010, pp. 356-361. 427 497

- M. B. Stuart, M. B. Stensgaard, and J. Sparso, "The 498 [6] 428 429 ReNoC reconfigurable network-on-chip: Architecture, 499 configuration algorithms, and evaluation," in ACM 500 430 501 Transactions on Embedded Computing Systems (TECS), 431 502 vol. 10, no. 4, New York, NY, USA, November 2011, pp. 432 45:1-45:26. 433 504

- [7] C. A. Nicopoulos, D. Park, J. Kim, M. S. Y. N. Vijaykrish-434 505 nan, and C. R. Das, "ViChaR: A dynamic virtual channel 506 435 regulator for network-on-chip routers," in Proceedings of 507 436 the 39th Annual IEEE/ACM International Symposium on 508 437 Microarchitecture (MICRO), Orlando, FL, December 2006, 509 438 510 pp. 333–346. 439

- 511 Y.-C. Lan, H.-A. Lin, S.-H. Lo, Y. H. Hu, and S.-J. Chen, 440 [8] 512 "A bidirectional NoC (BiNoC) architecture with dy-441 namic self-reconfigurable channel," *IEEE Transactions on* 513 442 Computer-Aided Design of Integrated Circuits and Systems, 515 443 vol. 30, no. 3, pp. 427-440, March 2011. 444 516

- [9] J. Hu and R. Marculescu, "DyAD smart routing for 517 445 networks-on-chip," in Proceedings of the 41st IEEE Design 518 446 Automation Conference (DAC), San Diego, CA, USA, July <sup>519</sup> 2004, pp. 260–263. 448

- 521 [10] R. Manevich, I. Cidon, A. Kolodny, and I. Walter, "Cen-449 522 tralized adaptive routing for NoCs," in IEEE Computer 450 523 Architecture Letters, vol. 9, no. 2, 2010, pp. 57–60. [11] N.-K. Dang, T.-V. Le-Van, and X.-T. Tran, "FPGA im-451

- 452 plementation of a low latency and high throughput 453 network-on-chip router architecture," in Proceedings of 454 the 2011 International Conference on Integrated Circuits and 455 Devices in Vietnam (ICDV), Hanoi, Vietnam, August 2011, 456 рр. 112–116. 457

- [12] C. J. Glass and L. M. Ni, "The turn model for 458 adaptive routing," Journal of the Association for Computing 459 *Machinery*, vol. 41, no. 5, pp. 874–902, September 1994. [Online]. Available: http://doi.acm.org/10.1145/185675. 460 461 185682 462

- T.-V. Le-Van, X.-T. Tran, and D.-T. Ngo, "Simulation [13] 463 and performance evaluation of a network-on-chip ar-chitecture based on SystemC," in *Proceedings of the 2012* 464 465 International Conference on Advanced Technologies for Com-466 467 munications (ATC), Hanoi, Vietnam, October 2012, pp. 170-175. 468

469

470

471

472

473

Thanh-Vu Le-Van was born in Hue, Vietnam. He received a Bachelor of Science degree in Physics from Hue University of Sciences - a member university of Hue University and a Master of Science degree from Vietnam National University Hanoi (VNU) in Electronics Engineering and Communications.

Currently, he is pursuing his Ph.D degree at VNU University of Engineering and Technology (VNU-UET), a member university of Vietnam National University, Hanoi (VNU).

He joined with the Key Laboratory for Smart Integrated Systems (SIS Lab) of VNU-UET in 2010. His research interests include Networkon-Chip (NoC), High-level modeling methods, Reconfigurable architecture.

He is a member of the IEEE (SSCS) and the Radio Electronics Association of Vietnam (REV).

Xuan-Tu Tran was born in Nghe An, Vietnam. He received a B.Sc. degree in 1999 from Hanoi University of Science and a M.Sc. degree in 2003 from Vietnam National University, Hanoi, all in Electronics Engineering and Communications; and a Ph.D. degree in 2008 from Grenoble INP (in collaboration with the CEA-LETI), France, in Micro Nano Electronics.

Xuan-Tu Tran is currently an associate professor at the Faculty of Electronics and

Telecommunications, VNU University of Engineering and Technology (VNU-UET), a member university of Vietnam National University, Hanoi (VNU). He has worked as a lecturer at Vietnam National University, Hanoi (1999-2003), as a research engineer at the CEA-LETI, MINATEC, France (2003-2008). He was an invited professor at the University Paris-Sud 11, France (2009, 2010), visiting professor at Grenoble INP in 2011. He is currently Deputy Director of UET-key Laboratory for Smart Integrated Systems (SIS) and Head of VLSI Systems Design laboratory. He is in charge for CoMoSy, VENGME, ReSoNoC projects for embedded systems and multimedia applications. His research interests include design and test of systems-on-chips, networks-on-chips, design-for-testability, asynchronous/synchronous VLSI design, low power techniques, and hardware architectures for multimedia applications.

He is a Senior Member of the IEEE, IEEE Circuits and Systems (CAS), IEEE Solid-State Circuits and Systems (SSCS), member of IEICE, and the Executive Board of the Radio Electronics Association of Vietnam (REV). He serves as Vice-Chairman of IEICE Vienam Section, Chairman of IEEE SSCS Vietnam Chapter. He also served as chair/co-chair and technical/organizing committee member for numerous international conferences (ATC, ICDV, IEEE DELTA, IEEE GIIS, ICCE, IEEE RIVF, IEEE APCCAS, IEEE ICCD, IEEE ICCAS, HP3C, NICS, APCC, ACOMP, CommandTel, ICGHIT...), Associate Editor-in-Chief of REV Journal on Electronics and Communications (JEC), Editor of VNU Journal of Computer Science and Communication Engineering (JCSCE), International Journal of Computing and Digital Systems (IJCDS).